辽宁WLCSP封装工艺

SiP具有以下优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。一个SiP可以选择性地包含无源器件、MEMS、光学元件以及其他封装和设备。辽宁WLCSP封装工艺

SIP类型,从目前业界SIP的设计类型和结构区分,SIP可分为以下几类。2D SIP,2D封装是指在基板的表面水平安装所有芯片和无源器件的集成方式。以基板(Substrate)上表面的左下角为原点,基板上表面所处的平面为XY平面,基板法线为Z轴,创建坐标系。2D封装方面包含FOWLP、FOPLP和其他技术。物理结构:所有芯片和无源器件均安装在基板平面,芯片和无源器件与XY平面直接接触,基板上的布线和过孔位于XY平面下方。电气连接:均需要通过基板(除了极少数通过键合线直接连接的键合点)。湖北MEMS封装SIP(System In Package,系统级封装)为一种封装的概念。

光电器件、MEMS 等特殊工艺器件的微小化也将大量应用 SiP 工艺。SiP 发展的难点随着 SiP 市场需求的增加,SiP 封装行业的痛点也开始凸显,例如无 SiP 行业标准,缺少内部裸片资源,SiP 研发和量产困难,SiP 模块和封装设计有难度。由于 SiP 模组中集成了众多器件,假设每道工序良率有一点损失,叠乘后,整个模组的良率损失则会变得巨大,这对封装工艺提出了非常高的要求。并且 SiP 技术尚属初级阶段,虽有大量产品采用了 SiP 技术,不过其封装的技术含量不高,系统的构成与在 PCB 上的系统集成相似,无非是采用了未经封装的芯片通过 COB 技术与无源器件组合在一起,系统内的多数无源器件并没有集成到载体内,而是采用 SMT 分立器件。

SiP还具有以下更多优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。SIP板身元件尺寸小,密度高,数量多,传统贴片机配置难以满足其贴片要求。

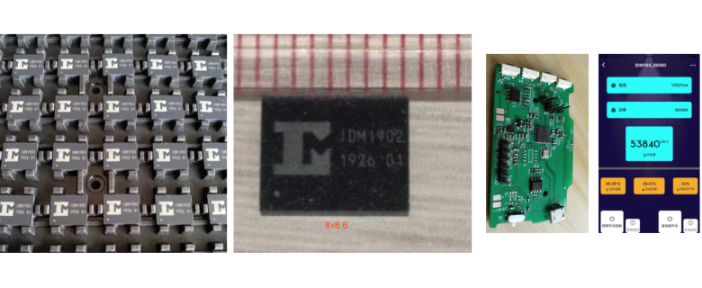

SiP 可以将多个具有不同功能的有源电子元件与可选无源器件,诸如 MEMS 或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,形成一个系统或者子系统。这么看来,SiP 和 SoC 极为相似,两者的区别是什么?能较大限度地优化系统性能、避免重复封装、缩短开发周期、降低成本、提高集成度。对比 SoC,SiP 具有灵活度高、集成度高、设计周期短、开发成本低、容易进入等特点。而 SoC 发展至今,除了面临诸如技术瓶颈高、CMOS、DRAM、GaAs、SiGe 等不同制程整合不易、生产良率低等技术挑战尚待克服外,现阶段 SoC 生产成本高,以及其所需研发时间过长等因素,都造成 SoC 的发展面临瓶颈,也造就 SiP 的发展方向再次受到普遍的讨论与看好。固晶贴片机(Die bonder),是封装过程中的芯片贴装(Die attach)的主要设备。江苏COB封装工艺

先进封装对于精度的要求非常高,因为封装中的芯片和其他器件的尺寸越来越小,而封装密度却越来越大。辽宁WLCSP封装工艺

SiP 封装优势:1)封装面积增大,SiP在同一个封装种叠加两个或者多个芯片。把垂直方向的空间利用起来,同时不必增加引出管脚,芯片叠装在同一个壳体内,整体封装面积较大程度上减少。2)采用超薄的芯片堆叠与TSV技术使得多层芯片的堆叠封装体积减小,先进的封装技术可以实现多层芯片堆叠厚度。3)所有元件在一个封装壳体内,缩短了电路连接,见笑了阻抗、射频、热等损耗影响。提高了光,电等信号的性能。4)SiP 可将不同的材料,兼容不同的GaAs,Si,InP,SiC,陶瓷,PCB等多种材料进行组合进行一体化封装。辽宁WLCSP封装工艺

上一篇: 江苏防震特种封装厂家

下一篇: 云南电子产品方案定制价格